- Liittynyt

- 14.10.2016

- Viestejä

- 24 940

Geekbenchin tulostietokannasta on löytynyt AMD:n Zen 6 -arkkitehtuuriin perustuvan Medusa Point -mobiiliprosessorin testitulos.

Testitulos itsessään ei kerro vielä paljoa, koska kyse on Engineering Sample -prosessorista ja se joko toimi peruskellotaajuutta matalammalla taajuudella tai Geekbench ei osannut tunnistaa sen kellotaajuuksia oikein. Testin mukaan 10-ytiminen Medusa Point sai 2 GHz:n kellotaajuudella yhdellä ytimellä 2300 ja kaikilla ytimillä 13002 pistettä, kun 10-ytiminen Strix Point yltää WCCFTechin kaivamien tulosten mukaan 5 GHz:n kellotaajuudella 2480 pisteeseen yhdellä ja 12445 pisteeseen kaikilla ytimillä.

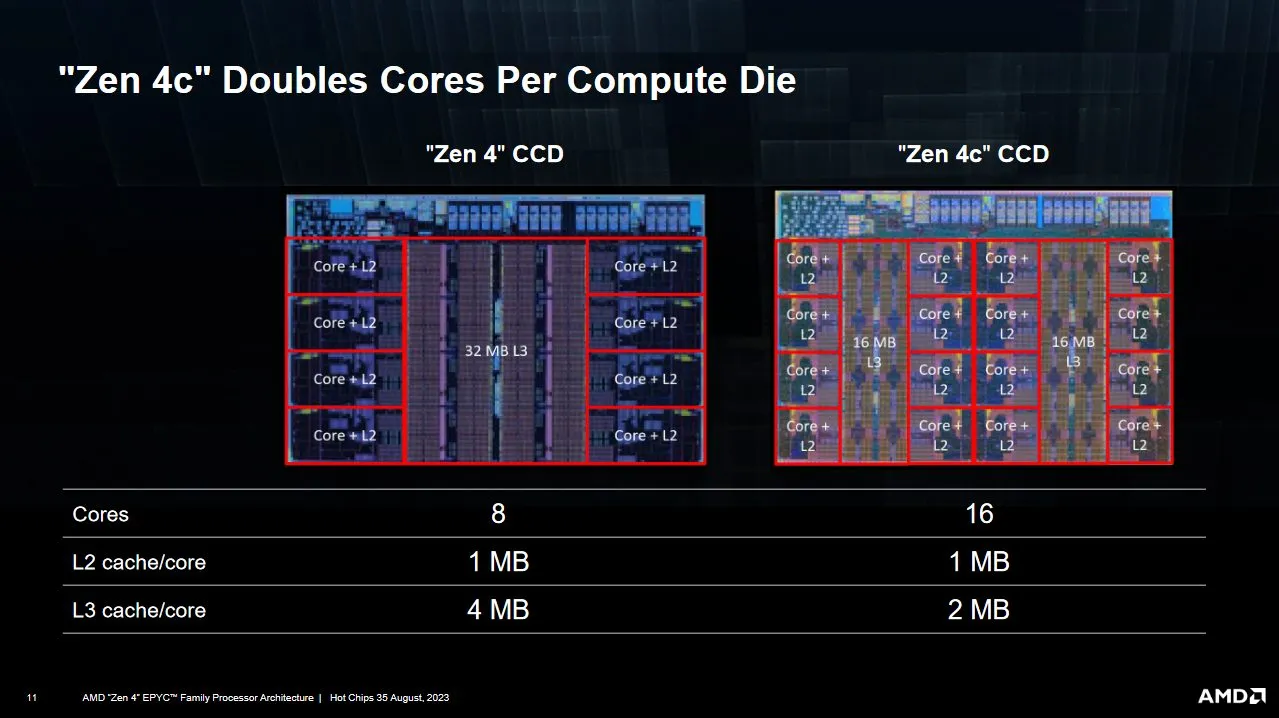

Testitulos paljastaa kuitenkin samalla, että 10-ytiminen ES-malli perustuu kahteen prosessorikompleksiin, joista ensimmäisessä on neljä ja jälkimmäisessä kuusi ydintä. Todennäköisimmin kyse on neljästä Zen 6- ja kuudesta Zen 6c -ytimestä. Lisäksi tulos paljastaa, että prosessori tukee AVX-VNNI-käskyjä ja sen myötä FP16-tarkkuutta.

Lähde: AMD Medusa Point Leak Shows 10 "Zen 6" Cores At 2 GHz Faster Than 10 "Zen 5" Cores at 5 GHz

Testitulos itsessään ei kerro vielä paljoa, koska kyse on Engineering Sample -prosessorista ja se joko toimi peruskellotaajuutta matalammalla taajuudella tai Geekbench ei osannut tunnistaa sen kellotaajuuksia oikein. Testin mukaan 10-ytiminen Medusa Point sai 2 GHz:n kellotaajuudella yhdellä ytimellä 2300 ja kaikilla ytimillä 13002 pistettä, kun 10-ytiminen Strix Point yltää WCCFTechin kaivamien tulosten mukaan 5 GHz:n kellotaajuudella 2480 pisteeseen yhdellä ja 12445 pisteeseen kaikilla ytimillä.

Testitulos paljastaa kuitenkin samalla, että 10-ytiminen ES-malli perustuu kahteen prosessorikompleksiin, joista ensimmäisessä on neljä ja jälkimmäisessä kuusi ydintä. Todennäköisimmin kyse on neljästä Zen 6- ja kuudesta Zen 6c -ytimestä. Lisäksi tulos paljastaa, että prosessori tukee AVX-VNNI-käskyjä ja sen myötä FP16-tarkkuutta.

Lähde: AMD Medusa Point Leak Shows 10 "Zen 6" Cores At 2 GHz Faster Than 10 "Zen 5" Cores at 5 GHz